香港中文大學 The Chinese University of Hong Kong

## Machine Learning in EDA: When and How

Bei Yu Department of Computer Science & Engineering Chinese University of Hong Kong

## Outline

1 When (machine learning integrated)

2 How (to solve unique challenges)

3 Future Direction

## Outline

1 When (machine learning integrated)

2 How (to solve unique challenges)

3 Future Direction

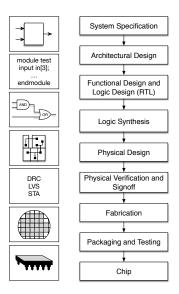

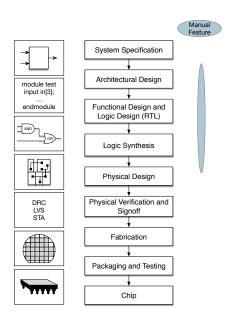

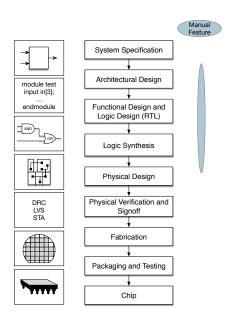

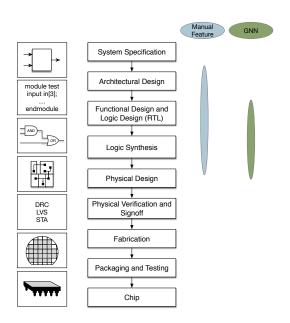

## When Machine Learning Integrated

## When Machine Learning Integrated

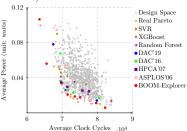

## RISC-V BOOM-Explorer [ICCAD'21 BPA]<sup>1</sup>

Table: Constraints of BOOM design specifications

| Rule | Descriptions                     |  |  |

|------|----------------------------------|--|--|

| 1    | FetchWdith ≥ DecodeWidth         |  |  |

| 2    | RobEntry   DecodeWidth +         |  |  |

| 3    | FetchBufferEntry > FetchWidth    |  |  |

| 4    | FetchBufferEntry   DecodeWidth   |  |  |

| 5    | fetchWidth = 2× ICacheFetchBytes |  |  |

| 6    | IntPhyRegister = FpPhyRegister   |  |  |

| 7    | LDQEntry = STQEntry              |  |  |

| 8    | MemIssueWidth = FpIssueWidth     |  |  |

|      |                                  |  |  |

\* The symbol "|" means RobEntry should be divisible by DecodeWidth

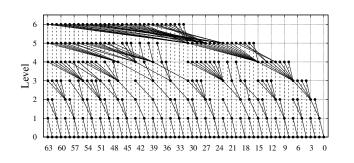

## Gaps Between Design Stages

## Case Study: Adder Design

- Logic synthesis v.s. physical synthesis

- Constraints mapping between two synthesis stages is difficult.

## Active Learning in Logic Synthesis [TCAD'19]<sup>2</sup>

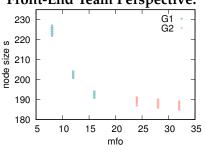

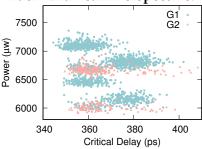

## **Back-End Team Perspective:**

- Run design tools with all solutions is time-consuming.

- For 3K solutions, running time is  $3000 \times 5 = 15$ K mins.

- What we care: Pareto Frontier Curve

## When Machine Learning Integrated

## When Machine Learning Integrated

## Example: Test Point Insertion [DAC'19]<sup>3</sup>

- Not every difficult-to-observe node has the same impact for improving the observability;

- Select the observation point locations with largest impact to minimize the total count.

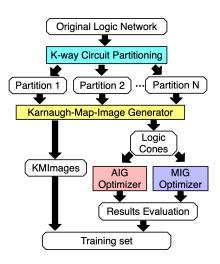

## Example: Logic Synthesis [ICCAD'19]<sup>4</sup>

Walter Lau Neto et al. (2019). "LSOracle: A logic synthesis framework driven by artificial intelligence". In: *Proc. ICCAD*, pp. 1–6.

## Example: Macro Block Placement [Nature'21]<sup>5</sup>

## When Machine Learning Integrated

## When Machine Learning Integrated

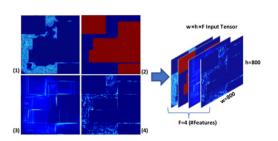

## RouteNet [ICCAD'18]6

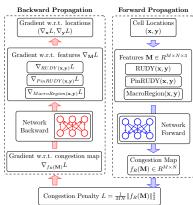

## **Features Extraction**

Input tensor constructed by stacking 2D features:

(1) Pin density, (2) macro (3) long-range RUDY, (4) RUDY pins

Input features for #DRV prediction. Red: macro region Green: global long-range RUDY Blue: global RUDY pins

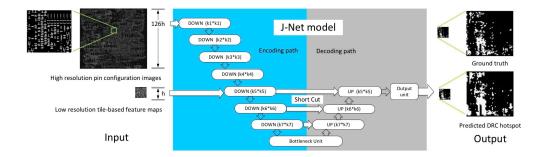

## J-Net [ISPD'20]<sup>7</sup>

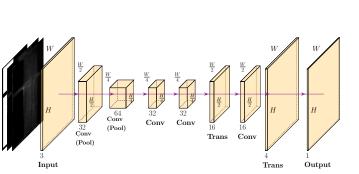

## CNN Driven Global Placement [DATE'21]<sup>8</sup>

## Machine learning vs. traditional EDA methodologies

|      | EDA Algorithms                                                                                                         | ML                                                                                                                           |

|------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|      | Placement, route, synthesis, CTS, simulations, etc                                                                     | Supervised, unsupervised, reinforcement learnings, etc                                                                       |

| Pros | Known optimality, robust, less<br>training data, good<br>interpretability,<br>Solve an abstract problem<br>efficiently | GPU parallel computing, easy to design, end-to-end training on complex problems, Solve any problem by learning from its data |

| Cons | Over simplification of dynamic, complex problems                                                                       | Rely too much on data, not leveraging the mechanics of the problem                                                           |

## Outline

1 When (machine learning integrated)

2 How (to solve unique challenges)

3 Future Direction

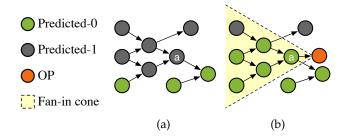

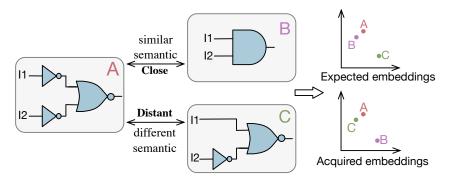

Challenge 1: Circuit Representation

## Defect of Previous GCN Works

- Previous works only focus on the graph structural information, which varies greatly across netlists.

- We should extract general knowledge!

Previous Structural GNN fail to capture the underlying semantic

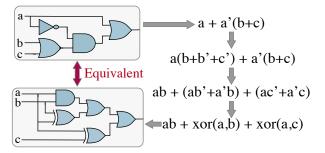

## Gate Functionality and Boolean Equivalence [DAC'22]<sup>9</sup>

## **Logic functionality**: keep the same across different designs.

Generalized to unseen netlists, even with totally different topology!

### Can we extract this information?

• **Yes!** -> **Key**: Boolean Equivalence

Ziyi Wang, Chen Bai, et al. (2022). "Functionality Matters in Netlist Representation Learning". 18/38

In: Proc. DAC.

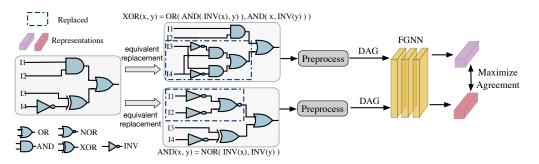

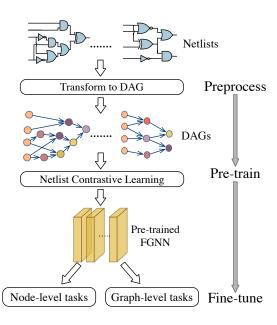

## Netlist Contrastive Learning Scheme

- Iterative random sub-netlist replacement.

- Positive sample pair share **same functionality**, while w. totally **different topology**.

- Maximizing agreement between positive samples: embedding of netlists with similar semantic (functionality) tend to be close

- Minimizing agreement between negative samples: distinguish from netlists with different semantic, even with similar topology.

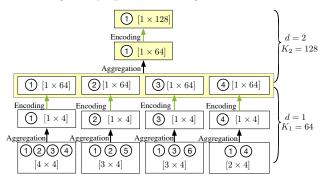

## Pre-trained Circuit Learning Model

# Challenge 2: Timing Modeling

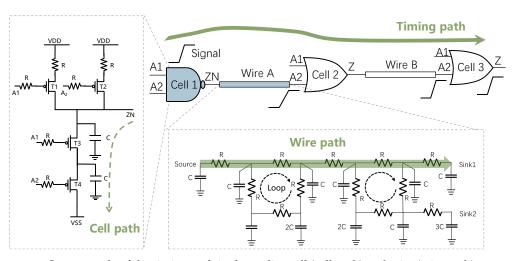

## Timing Model in EDA

One example of the timing path in the netlist, cell (cell path) and wire (wire path).

## Why GCN cannot model timing well?

- Timing needs to capture path information

- GCN is only good at node embedding and graph embedding

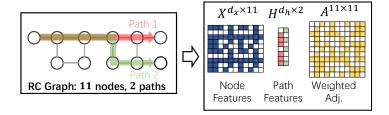

## Current Progress: Wire Timing [DATE'23]<sup>10</sup>

### The RC net graph $\mathcal{G}$ is represented with:

- Node feature matrix *X* for each capacitance

- Path feature matrix *H* for each wire path

- Weighted adj. matrix *A* for each resistance

- Label matrix for real wire slew and delay

Yuyang Ye et al. (2023). "Fast and Accurate Wire Timing Estimation Based on Graph Learning".

In: *Proc. DATE*. 24/38

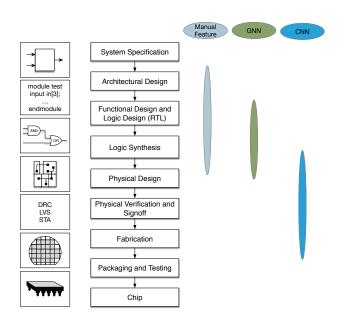

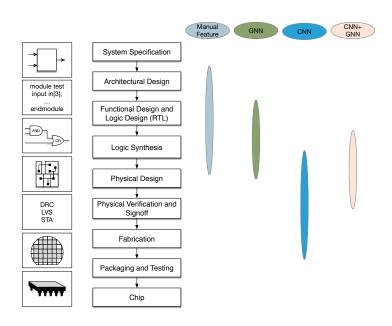

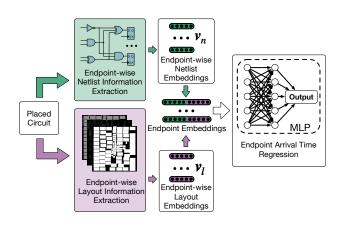

## Challenge 3: Netlist+Layout: Multimodality

## Netlist+Layout: Multimodality

## Netlist+Layout: Multimodality

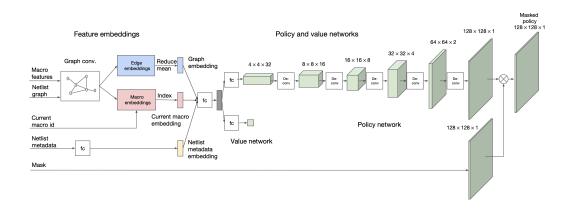

## GCN + CNN Flow [DAC'23]<sup>11</sup>

- Customized GNN: extract information from netlists

- CNN with novel masking technique: extract information from layouts.

Ziyi Wang, Siting Liu, et al. (2023). "Realistic Sign-off Timing Prediction via Multimodal Fusion". In: *Proc. DAC*.

## Challenge 4: Constrained AIGC

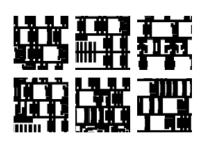

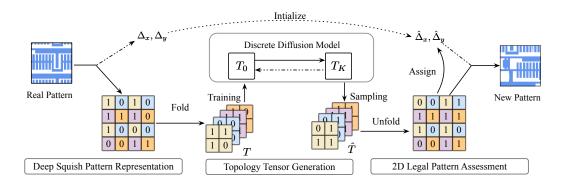

## Layout Pattern Generation

Original Layout Patterns [ICCAD'20]

Generated Layout Patterns (Ours)

VLSI layout patterns provide critical resources in various designs for manufacturability research, from early technology node development to back-end design and sign-off flows DAC'19]<sup>12</sup>.

<sup>&</sup>lt;sup>12</sup>Haoyu Yang et al. (2019). "DeePattern: Layout pattern generation with transforming convolutional auto-encoder". In: *DAC*, pp. 1–6.

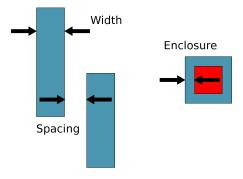

## An End-to-End Learning Solution?

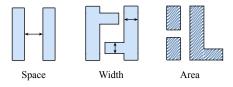

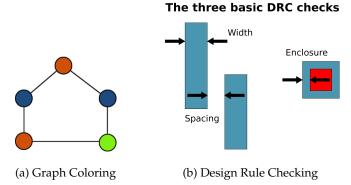

### The three basic DRC checks

- Maybe No

- Gap between Discrete Rules and Continuous DNN Model

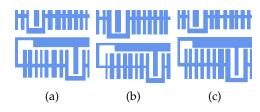

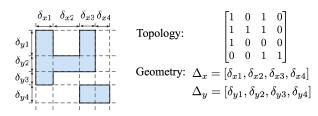

## Squish Pattern Representation

## Squish Pattern [US Patent'14]<sup>13</sup>

- Lossless and efficient representation method

- Encodes layout into pattern topology matrix and geometric information

- Problem #1: information density of each pixel is still not satisfactory

## Pattern Legalization

Examples of DRC Rule

#### Finding legal distance vector for each topology

- Solving a Linear System (1D pattern) [DAC'19].

- Using Exist Distance Vector (2D pattern) [ICCAD'20]

- Problem #3: 2D pattern introduces non-linear constraint, hard to solve!

## Constrained AIGC [DAC'23]<sup>14</sup>

Zixiao Wang et al. (2023). "DiffPattern: Layout Pattern Generation via Discrete Diffusion". In:  $Proc.\ DAC$ .

### Outline

1 When (machine learning integrated)

2 How (to solve unique challenges)

3 Future Direction

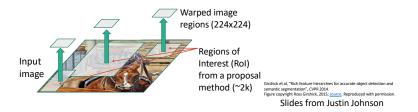

R-CNN: Region-Based CNN

Girshick et al, "Rich feature hierarchies for accurate object detection and semantic segmentation", CVPR 2014.

Figure copyright Ross Girshick, 2015; source. Reproduced with permission.

Slides from Justin Johnson

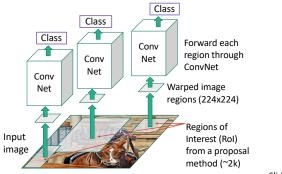

R-CNN: Region-Based CNN

Regions of Interest (RoI) from a proposal method (~2k)

Girshick et al. "Rich feature hierarchies for accurate object detection and semantic segmentation", CVPR 2014.

Figure copyright Ross Girshick, 2015; source. Reproduced with permission.

Slides from Justin Johnson

R-CNN: Region-Based CNN

Classify each region

Slides from Justin Johnson

Slides from Justin Johnson

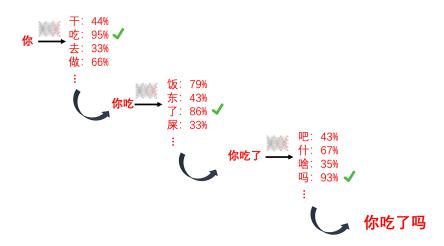

#### How Machine Can Understand Text?

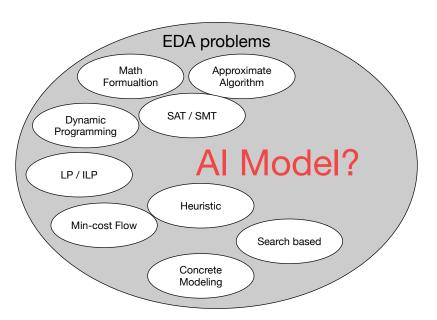

## Challenges to AI

- Combinatorial Problem (e.g. Coloring)

- Handling Complicated Rules

## Know the Boundary!

## Know the Boundary!

# **THANK YOU!**