#### **CENG3420**

# Lab 3-1: RISCV-LC Datapath

#### Chen BAI

Department of Computer Science and Engineering

The Chinese University of Hong Kong

cbai@cse.cuhk.edu.hk

Spring 2021

香港中文大學 The Chinese University of Hong Kong

### Overview

Introduction

Background

Lab3-1 Assignmen

### LC-3b

- LC-3b: **Little Computer 3, b** version.

- Relatively simple instruction set

- Most used in teaching for CS & CE

- Developed by Yale Patt@UT & Sanjay J. Patel@UIUC

#### RISCV-LC

- Inspired from LC-3b

- ► RISC-V version (RV32I)

- Programming language: C

- Compatible with Lab2 (RV32I assembler & RV32I simulator)

#### RISCV-LC

- RISC-V 32 general-purpose registers

- 32-bit data and address

- 28+ instructions (including pseudo instructions)

#### Plus 4 special-purpose registers:

- Program Counter (PC)

- Instruction Register (IR)

- Memory Access Register (MAR)

- Memory Data Register (MDR)

In order to make labs easy, I have modified some definitions of instructions, and they do not oberseve RISC-V specifications strictly!

### Overview

Introduction

Background

Lab3-1 Assignmen

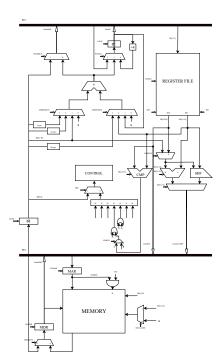

# Datapath

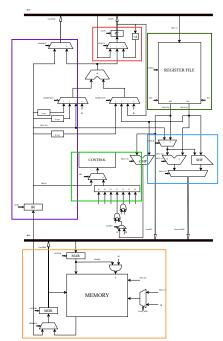

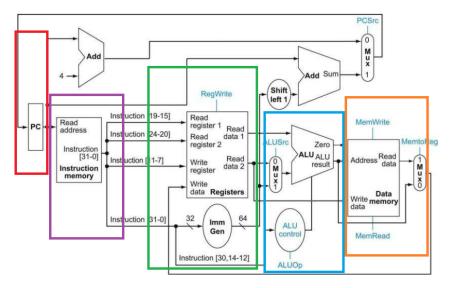

# **Datapath Annotation**

# **Datapath Annotation**

RISCV datapath annotation based on the textbook

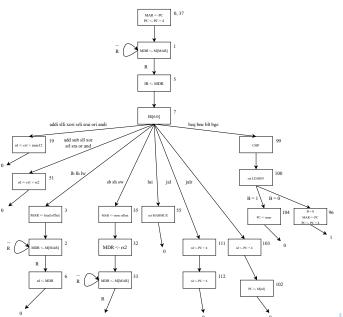

#### **FSM**

- Clock cycle: The cycle time of a microprocessor is the duration of a clock cycle

- ► Finite State Machine: The behavior of the RISCV-LC microarchitecture during a given clock cycle is completely determined by the 33 control signals. These 33 control signals specify the state of the control structure of the RISCV-LC microarchitecture.

### **FSM**

### Overview

Introduction

Background

Lab3-1 Assignment

# Operations in One Clock Cycle

```

In "riscy-lc.c":

void cycle() {

eval_micro_sequencer();

cycle_memory();

eval bus drivers();

drive bus();

latch_datapath_values();

CURRENT LATCHES = NEXT LATCHES;

CYCLE COUNT++;

```

### Lab3.1 Assignment

RISCV-LC codes will be released on 21 Apr.

- git clone https://github.com/baichen318/ceng3420.git; cd ceng3420

- git checkout lab3.1

Compile (Linux + x86\_64 environment is suggested)

make

Run the simulator

./lc uop benchmarks/isa.bin # RISCV-LC runs isa.bin

## Lab3.1 assignment

- Complete uop (i.e., fill x with right 1s or 0s)

- Finish eval\_micro\_sequencer

These unimplemented codes are annotated with Lab3-1 assignment

## Lab3.1 assignment

Verify your codes with binary machine codes suffixed with .bin

- ► isa.bin

- count10.bin

- swap.bin

#### Submission Method:

Submit the source code and report after the whole Lab3, onto blackboard.

### Thanks. For any question:

byu@cse.cuhk.edu.hk cbai@cse.cuhk.edu.hk ybai@cse.cuhk.edu.hk