香港中文大學 The Chinese University of Hong Kong

### **CENG3420**

### Lab 2-2: RISC-V RV32I Simulator

Chen BAI Department of Computer Science & Engineering Chinese University of Hong Kong cbai@cse.cuhk.edu.hk

Spring 2022

2 RV32I Instructions

3 Lab 2-2 Assigment

## Introduction

#### Assembler

• Turn symbols into machine binary instructions, *e.g.*, lc3b\_asm, riscv64-unknown-elf-as, ...

#### Simulator

• Mimic the behavior of a processor, *e.g.*, lc3b\_sim, spike, QEMU, rv8, ...

# Introduction LC-3b

- LC-3b: Little Computer 3, b version.

- Relatively simple instruction set

- Most used in teaching for CS & CE

- Developed by Yale Patt@UT & Sanjay J. Patel@UIUC

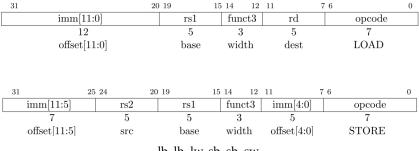

## **RV32I Instructions**

| 31 30 25                                          | 24 21   | 20     | 19  | 15  14   | 12  | 11 8                      | 7                        | 6    | 0         |

|---------------------------------------------------|---------|--------|-----|----------|-----|---------------------------|--------------------------|------|-----------|

| funct7                                            | rs2     |        | rs1 | func     | et3 | re                        | 1                        | opco | de R-type |

|                                                   |         |        |     |          |     |                           |                          |      |           |

| imm[1                                             | 1:0]    |        | rs1 | func     | et3 | re                        | 1                        | opco | de I-type |

|                                                   |         |        |     |          |     |                           |                          |      |           |

| imm[11:5]                                         | rs2     |        | rs1 | func     | et3 | imm                       | [4:0]                    | opco | de S-type |

|                                                   |         |        |     |          |     |                           |                          |      |           |

| $\operatorname{imm}[12] \operatorname{imm}[10:5]$ | rs2     |        | rs1 | func     | et3 | $\operatorname{imm}[4:1]$ | $\operatorname{imm}[11]$ | opco | de B-type |

|                                                   |         |        |     |          |     |                           |                          |      |           |

|                                                   | imm[31: | 12]    |     |          |     | re                        | 1                        | opco | de U-type |

|                                                   |         |        |     |          |     |                           |                          |      |           |

| [imm[20]] $imm[10]$                               | 0:1] i  | mm[11] | imr | n[19:12] |     | re                        | 1                        | opco | de J-type |

RV32I instructions base formats.

# Integer Computational Instructions

| 31                                                                                                                                                    | 2                           | 0 19            | 15 14               | 12 11           | 7 6                   | 0 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|---------------------|-----------------|-----------------------|---|

| imm[11:0]                                                                                                                                             |                             | rs1             | funct3              | rd              | opcode                |   |

| 12                                                                                                                                                    | 5                           | 3               | 5                   | 7               |                       |   |

| I-immediate[11:0]                                                                                                                                     |                             | src             | ADDI/SLTI[U         | J] dest         | OP-IMM                |   |

| I-immedia                                                                                                                                             | I-immediate[11:0]           |                 | ANDI/ORI/X          | ORI dest        | OP-IMM                |   |

|                                                                                                                                                       |                             | addi, a         | ındi, ori, xori     |                 |                       |   |

| 31 25 24 20 19 15 14 12 11 7 6                                                                                                                        |                             |                 |                     |                 |                       |   |

| 31 25 2                                                                                                                                               | 24 20 1                     | 9 15            | 5 14 12             | 11 7            | 6                     | 0 |

| $\frac{31}{11:5}$                                                                                                                                     | 24 20 1<br>imm[4:0]         | 9 15<br>rs1     | 5 14 12<br>funct3   | 11 7<br>rd      | opcode                | 0 |

|                                                                                                                                                       |                             |                 | 1                   |                 |                       | 0 |

| imm[11:5]<br>7                                                                                                                                        | imm[4:0]                    | rs1             | funct3              | rd              |                       | 0 |

| imm[11:5]<br>7<br>0000000                                                                                                                             | imm[4:0]<br>5               | rs1<br>5        | funct3<br>3         | rd<br>5         | opcode<br>7           | 0 |

| $\begin{tabular}{ c c c c c } \hline $imm[11:5] \\ \hline $7$ \\ 00000000 \\ 00000000 \\ \hline $00000000 \\ $00000000 \\ end{tabular} \end{tabular}$ | imm[4:0]<br>5<br>shamt[4:0] | rs1<br>5<br>src | funct3<br>3<br>SLLI | rd<br>5<br>dest | opcode<br>7<br>OP-IMM | 0 |

| 31 12              | 2 11 7                | 7 6 0  |

|--------------------|-----------------------|--------|

| imm[31:12]         | rd                    | opcode |

| 20                 | 5                     | 7      |

| U-immediate[31:12] | $\operatorname{dest}$ | LUI    |

| U-immediate[31:12] | dest                  | AUIPC  |

#### Integer Computational Instructions Integer Register-Register Instructions

| 31 | 25      | 24 20                 | 19 15                 | 5 14 12     | 11 7   | 6      | 0 |

|----|---------|-----------------------|-----------------------|-------------|--------|--------|---|

|    | funct7  | rs2                   | rs1                   | funct3      | rd     | opcode |   |

|    | 7       | 5                     | 5                     | 3           | 5      | 7      |   |

|    | 0000000 | $\operatorname{src2}$ | $\operatorname{src1}$ | ADD/SLT/SLT | U dest | OP     |   |

|    | 0000000 | $\operatorname{src2}$ | $\operatorname{src1}$ | AND/OR/XOR  | dest   | OP     |   |

|    | 0000000 | $\operatorname{src2}$ | src1                  | SLL/SRL     | dest   | OP     |   |

|    | 0100000 | src2                  | src1                  | SUB/SRA     | dest   | OP     |   |

add, and, or, xor, sll, srl, sub, sra

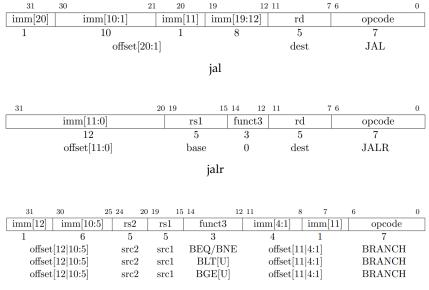

#### Control Transfer Instructions Unconditional Branches & Conditional Branches

beq, bne, blt, bge

#### Load and Store Instructions

lb, lh, lw, sb, sh, sw

# Lab 2-2 Assignment

#### Lab 2-2 Assignment Pre-requisites

#### Get Latest Updates of the Lab

- Click https://github.com/baichen318.

- Follow my GitHub account. Follow me through GitHub, so that you can see any latest updates of the lab!

| Why GitHub? V Team Enterprise                                                                              | Explore $\lor$ Marketplace Pricing $\lor$                                                                                                                                                                                                                                                                                                                                                         | Search / Sign in Sign up                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1997                                                                                                       | 🔟 Overview 🔒 Repositories 👀 🖽 Projects 🛞 i                                                                                                                                                                                                                                                                                                                                                        | Packages 🛱 Stars (25)                                                                                                                                                                                                       |

|                                                                                                            | Popular repositories                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                             |

|                                                                                                            | FreePDK45 Public   This is no FinePDK45 V1.4 Process Development Kit for the 45 nm technology ••••••••••••••••••••••••••••••••••••                                                                                                                                                                                                                                                                | ham (Public)<br>Tokas frain quasi-spinn<br>Dasse dee latenting complex stack for equ, gau and specialized<br>constrations<br>● Pythem Sr2 S 1                                                                               |

| Chen BAI<br>baichen 318<br>Fallow                                                                          | vin.config (Public)   My own cester coeffigurations for the Vin editor (Public)   • Vin script $\dot{\Omega}$ 3                                                                                                                                                                                                                                                                                   | Chipyand (Public)   Foreid firm undi-schlingerd (Public)   Aug & Bitto C-V Sido (Design Firmework with In-Inder come, out-of-<br>order come, count-of-<br>order come, count-of-<br>order come, count-of- (Public)   C \$2 2 |

| A: 18 followers - 19 following<br>(1) The Chinese University of Hong Kong<br>Phtps://buichen318.github.iq/ | Rampberry-PI-SmartCar (Public)<br>A smart cur controlled by Riapberry PI, can recognize images through<br>Temoritor                                                                                                                                                                                                                                                                               | onni_tool (Public)<br>A general tool for ONNX moduls                                                                                                                                                                        |

| Achievements                                                                                               | ● Python 😭 1                                                                                                                                                                                                                                                                                                                                                                                      | ● Python 🖙 1                                                                                                                                                                                                                |

| <b>&gt;</b>                                                                                                | 20 contributions in the last year                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                             |

| Highlights<br>☆ (mp)<br>Block or Report                                                                    | H3 Max H4 Max |                                                                                                                                                                                                                             |

#### Lab 2-2 Assignment Pre-requisites

#### Get the RV32I Simulator

- \$ git clone https://github.com/baichen318/ceng3420.git

- \$ cd ceng3420

- \$ git checkout lab2.2

Compile (Linux/MacOS environment is suggested)

• \$ make

#### Run the Simulator

• \$ ./sim benchmarks/count10.bin # the simulator can execute successfully if you have implemented it.

#### Finish the RISCV LC simulator including 25 instructions in sim.c

- Integer Register-Immediate Instructions: slli, xori, srli, srai, ori, andi, lui

- Integer Register-Register Operations: sub, sll, xor, srl, sra, or, and

- Unconditional Jumps: jalr, jal

- Conditional Branches: bne, blt, bge

- Load and Store Instructions: lb, lh, lw, sb, sh, sw

These unimplemented codes are commented with Lab2-2 assignment.

#### Lab 2-2 Assignment Verification

#### Benchmarks

Verify your codes with these benchmarks (inside the benchmarks directory)

- isa.bin

- count10.bin

- swap.bin

#### Verification

- isa.bin  $\rightarrow$  a3 = -18/0xffffffee and MEMORY[0x84 + 16] = 0xffffffee

- count10.bin  $\rightarrow$  t2 = 55/0x0000037

- swap.bin  $\rightarrow$  NUM1 changes from 0xabcd to 0x1234 and NUM2 changes from 0x1234 to 0xabcd

#### Submission Method:

#### Submit the source code and report into Blackboard, including

- Your implementations, *i.e.*, asm.c, and *sim.c* with the name of name-sid-lab2-1.c and name-sid-lab2-2.c (*e.g.*, zhangsan-1234567890-lab2-1.c, zhangsan-1234567890-lab2-2.c, *etc.*)

- A lab report (name-sid-lab2.pdf) illustrates your implementation for two parts of Lab 2 and all console results (screenshots).

- Deadline: 23:59, 31 Mar (Thu)

#### Tips

Inside docs, there are three valuable documents for your reference!

- opcodes-rv32i: RV32I opcodes

- riscv-spec-20191213.pdf: RV32I specifications

- risc-v-asm-manual.pdf: RV32I assembly programming manual