# CENG 3420 Computer Organization and Design Lecture 05: ALU Review

#### Bei Yu

#### 香港中文大學 The Chinese University of Hong Kong

CEG3420 L05.1

#### **MIPS Representations**

#### □ 32-bit signed numbers (2's complement):

```

0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000_{two} = 0_{ten}

maxint

1111 \ 1111_{two} = + 2,147,483,647_{ten}

0111

1111 1111 1111 1111 1111

0000 \ 0000 \ 0000 \ 0000_{two} = -2,14 \overline{k},483,648_{ten}

1000

0000 0000

1000 0000 0000 0000 0000 0000 0000 0001_{two} = -2,147 \times 483,647_{ten}

0000 \ 0000 \ 0010_{two} = -2,147,483,646_{ten}

1000 0000 0000 0000 0000

minint

1111 \ 1110_{two} = - 2_{ten}

1111

1111

1111

1111 1111 1111

1111 1111 1111 1111 1111_{two} = -1_{ten}

1111

1111 1111

```

What if the bit string represented addresses?

need operations that also deal with only positive (unsigned) integers

CEG3420 L05.2

#### **Two's Complement Operations**

- Negating a two's complement number complement all the bits and then add a 1

- remember: "negate" and "invert" are quite different!

- Converting n-bit numbers into numbers with more than n bits:

- MIPS 16-bit immediate gets converted to 32 bits for arithmetic

- sign extend copy the most significant bit (the sign bit) into the other bits

0010 -> 0000 0010 1010 -> 1111 1010

• sign extension versus zero extend (lb vs. lbu)

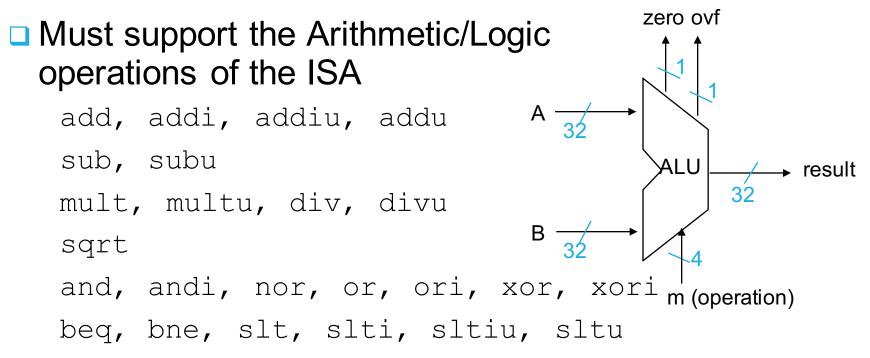

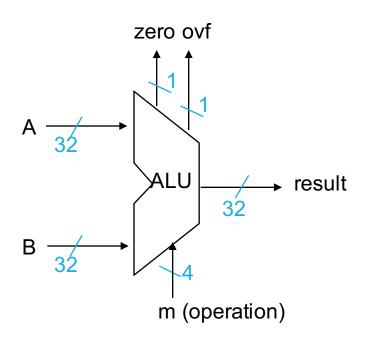

# **Design the MIPS Arithmetic Logic Unit (ALU)**

#### With special handling for

- sign extend addi, addiu, slti, sltiu

- > zero extend andi, ori, xori

- Overflow detected add, addi, sub

#### **MIPS Arithmetic and Logic Instructions**

|         | 31 | 25 | 20 | 15 |         | 5 0   |

|---------|----|----|----|----|---------|-------|

| R-type: | ор | Rs | Rt | Rd |         | funct |

|         |    |    |    |    |         |       |

| I-Type: | ор | Rs | Rt | In | nmed 10 | 6     |

| Туре  | ор     | funct |

|-------|--------|-------|

| ADDI  | 001000 | хх    |

| ADDIU | 001001 | XX    |

| SLTI  | 001010 | XX    |

| SLTIU | 001011 | хх    |

| ANDI  | 001100 | хх    |

| ORI   | 001101 | XX    |

| XORI  | 001110 | XX    |

| LUI   | 001111 | xx    |

| Туре | ор     | funct  |

|------|--------|--------|

| ADD  | 000000 | 100000 |

| ADDU | 000000 | 100001 |

| SUB  | 000000 | 100010 |

| SUBU | 000000 | 100011 |

| AND  | 000000 | 100100 |

| OR   | 000000 | 100101 |

| XOR  | 000000 | 100110 |

| NOR  | 000000 | 100111 |

| Туре | ор     | funct  |

|------|--------|--------|

|      | 000000 | 101000 |

|      | 000000 | 101001 |

| SLT  | 000000 | 101010 |

| SLTU | 000000 | 101011 |

|      | 000000 | 101100 |

# **Design Trick: Divide & Conquer**

- Break the problem into simpler problems, solve them and glue together the solution

- Example: assume the immediates have been taken care of before the ALU

- now down to 10 operations

- can encode in 4 bits

| 0 | add  |

|---|------|

| 1 | addu |

| 2 | sub  |

| 3 | subu |

| 4 | and  |

| 5 | or   |

| 6 | xor  |

| 7 | nor  |

| а | slt  |

| b | sltu |

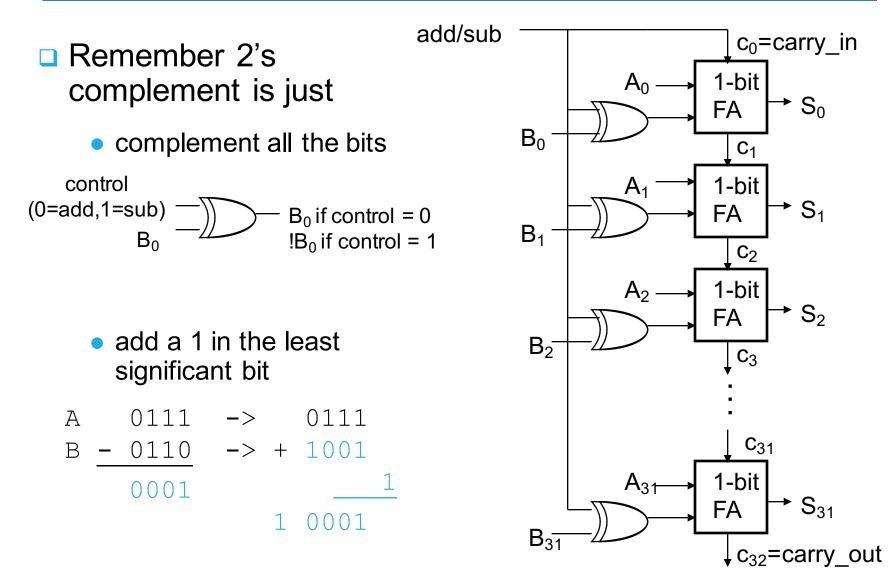

#### **Addition & Subtraction**

#### Just like in grade school (carry/borrow 1s)

| -      |        |        |

|--------|--------|--------|

| 0111   | 0111   | 0110   |

| + 0110 | - 0110 | - 0101 |

| 1101   | 0001   | 0001   |

Two's complement operations are easy

do subtraction by negating and then adding

| 0111   | -> | 0111   |

|--------|----|--------|

| - 0110 | -> | + 1010 |

| 0001   |    | 1 0001 |

Overflow (result too large for finite computer word)

- e.g., adding two n-bit numbers does not yield an n-bit number

0111

- + 0001

1000

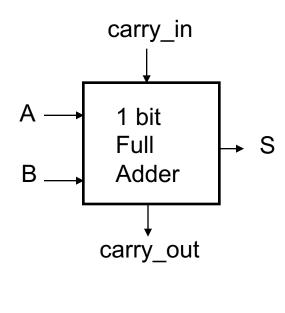

#### **Building a 1-bit Binary Adder**

| Α | В | carry_in | carry_out | S |

|---|---|----------|-----------|---|

| 0 | 0 | 0        | 0         | 0 |

| 0 | 0 | 1        | 0         | 1 |

| 0 | 1 | 0        | 0         | 1 |

| 0 | 1 | 1        | 1         | 0 |

| 1 | 0 | 0        | 0         | 1 |

| 1 | 0 | 1        | 1         | 0 |

| 1 | 1 | 0        | 1         | 0 |

| 1 | 1 | 1        | 1         | 1 |

S = A xor B xor carry\_in carry\_out = A&B | A&carry\_in | B&carry\_in (majority function)

□ How can we use it to build a 32-bit adder?

How can we modify it easily to build an adder/subtractor?

CEG3420 L05.8

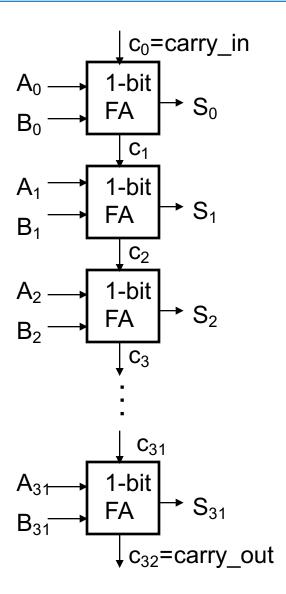

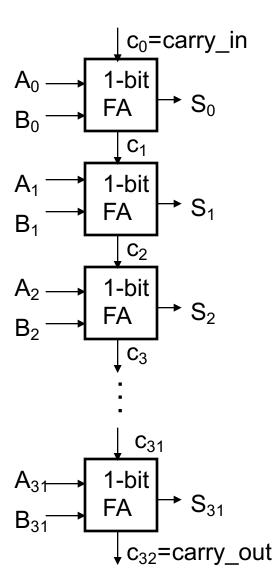

Just connect the carry-out of the least significant bit FA to the carry-in of the next least significant bit and connect ...

Ripple Carry Adder (RCA)

- advantage: simple logic, so small (low cost)

- disadvantage: slow and lots of glitching (so lots of energy consumption)

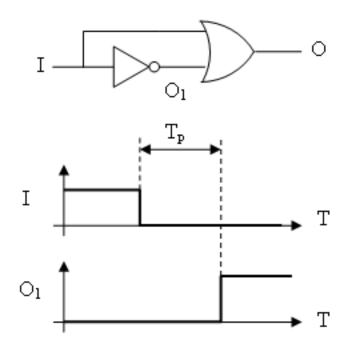

#### Glitch

- Glitch: invalid and unpredicted output that can be read by the next stage and result in a wrong action

- **Example:** Draw the propagation delay

# **Glitch in RCA**

| Α | В | carry_in | carry_out | S |

|---|---|----------|-----------|---|

| 0 | 0 | 0        | 0         | 0 |

| 0 | 0 | 1        | 0         | 1 |

| 0 | 1 | 0        | 0         | 1 |

| 0 | 1 | 1        | 1         | 0 |

| 1 | 0 | 0        | 0         | 1 |

| 1 | 0 | 1        | 1         | 0 |

| 1 | 1 | 0        | 1         | 0 |

| 1 | 1 | 1        | 1         | 1 |

#### **But What about Performance?**

Critical path of n-bit ripple-carry adder is n\*CP

Design trick – throw hardware at it (Carry Lookahead)

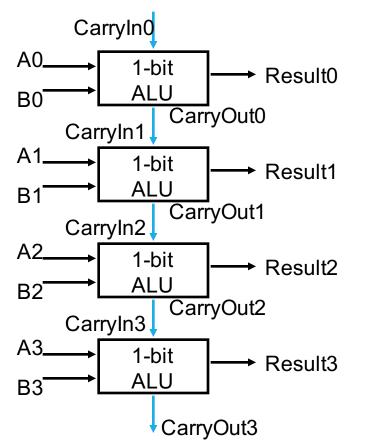

#### A 32-bit Ripple Carry Adder/Subtractor

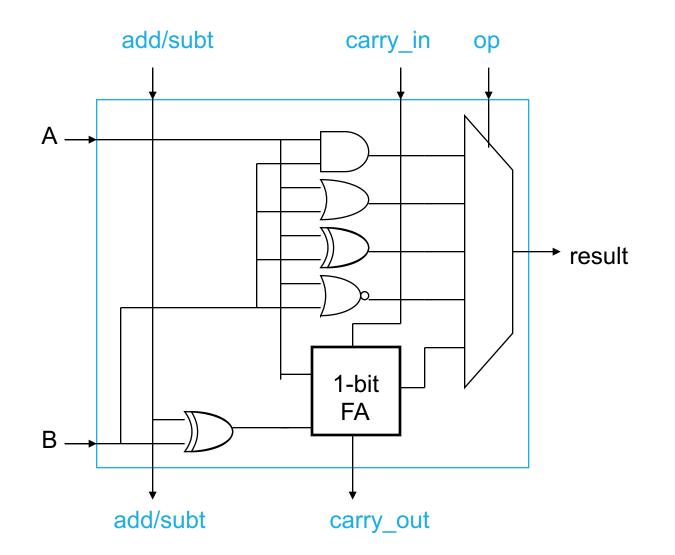

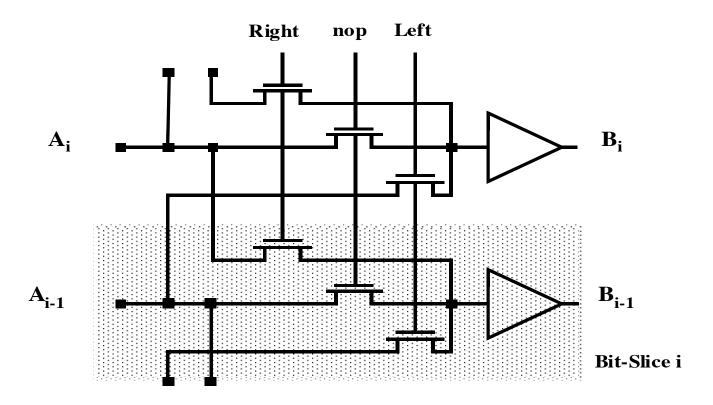

#### A Simple ALU Cell with Logic Op Support

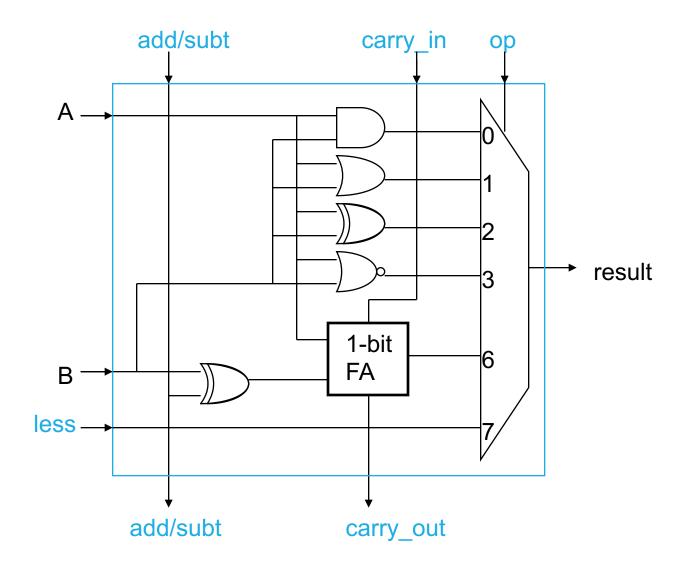

#### Modifying the ALU Cell for slt

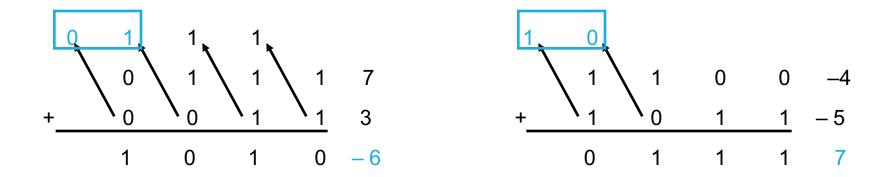

#### **Overflow Detection**

Overflow occurs when the result is too large to represent in the number of bits allocated

- adding two positives yields a negative

- or, adding two negatives gives a positive

- or, subtract a negative from a positive gives a negative

- or, subtract a positive from a negative gives a positive

□ On your own: Prove you can detect overflow by:

Carry into MSB xor Carry out of MSB

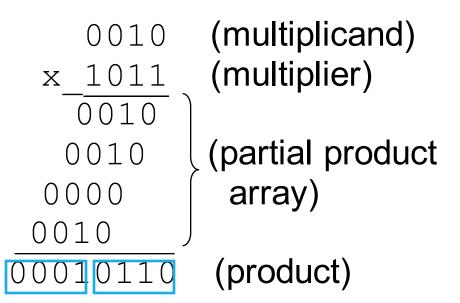

## **Multiplication**

#### More complicated than addition

Can be accomplished via shifting and adding

Double precision product produced

More time and more area to compute

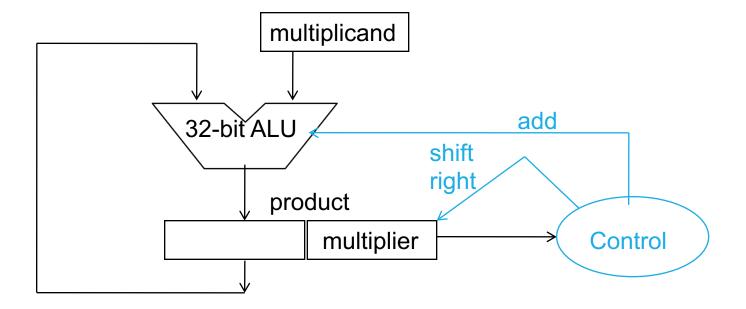

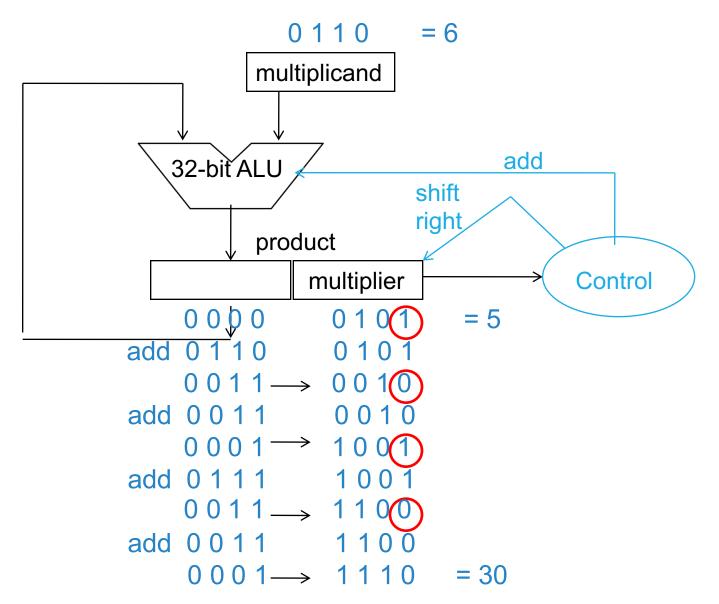

#### Add and Right Shift Multiplier Hardware

#### Add and Right Shift Multiplier Hardware

#### **MIPS Multiply Instruction**

# Multiply (mult and multu) produces a double precision product

mult \$s0, \$s1 # hi||lo = \$s0 \* \$s1

- Low-order word of the product is left in processor register

lo and the high-order word is left in register hi

- Instructions mfhi rd and mflo rd are provided to move the product to (user accessible) registers in the register file

- Multiplies are usually done by fast, dedicated hardware and are much more complex (and slower) than adders

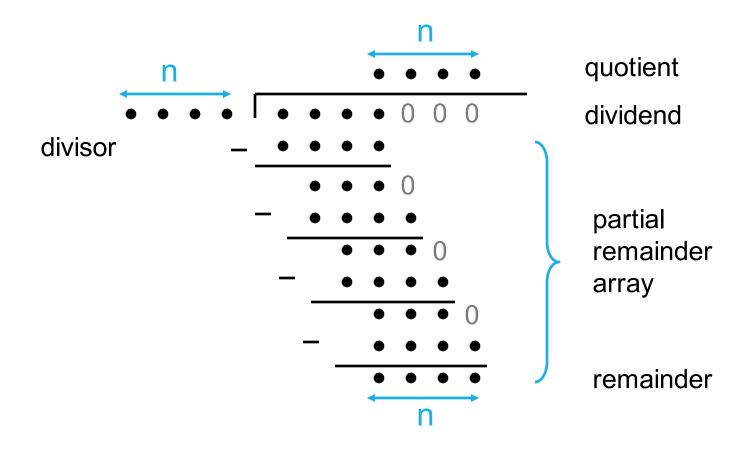

#### **Division**

Division is just a *bunch* of quotient digit guesses and left shifts and subtracts

#### **Example: Division**

#### Dividing 1001010 by 1000

#### **MIPS Divide Instruction**

- Divide generates the reminder in hi and the quotient in 10

- div \$s0, \$s1 # lo = \$s0 / \$s1

# hi = \$s0 mod \$s1

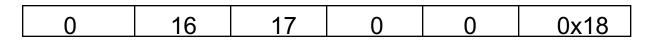

| op rs | rt | rd | shamt | funct |

|-------|----|----|-------|-------|

|-------|----|----|-------|-------|

- Instructions mflo rd and mfhi rd are provided to move the quotient and reminder to (user accessible) registers in the register file

- As with multiply, divide ignores overflow so software must determine if the quotient is too large. Software must also check the divisor to avoid division by 0.

...

**Representing Big (and Small) Numbers**

What if we want to encode the approx. age of the earth?

4,600,000,000 or 4.6 x 10<sup>9</sup>

There is no way we can encode either of the above in a 32-bit integer.

□ Floating point representation (-1)<sup>sign</sup> x F x 2<sup>E</sup>

• Still have to fit everything in 32 bits (single precision)

| ;   | s   | Ε ( | exponent) | F (fract | ion) |

|-----|-----|-----|-----------|----------|------|

| 1 b | oit |     | 8 bits    | 23 bits  |      |

• The base (2, not 10) is hardwired in the design of the FPALU

More bits in the fraction (F) or the exponent (E) is a trade-off between precision (accuracy of the number) and range (size of the number)

#### **Exception Events in Floating Point**

- Overflow (floating point) happens when a positive exponent becomes too large to fit in the exponent field

- Underflow (floating point) happens when a negative exponent becomes too large to fit in the exponent field

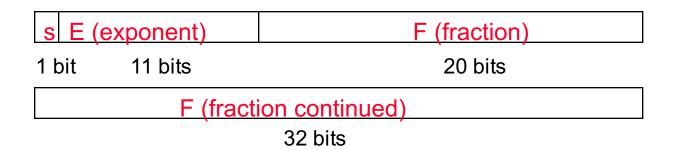

□One way to reduce the chance of underflow or overflow is to offer another format that has a larger exponent field

Double precision – takes two MIPS words